An IATF 16949, ISO9001 and ISO 14001 Certified Company

# **6 Amp TRIACs**

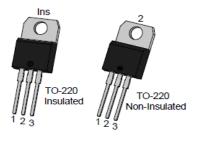

TO-220

BTA06 (Insulated)

BTB06 (Non-Insulated)

TO-220 Plastic Package RoHS compliant

#### **GENERAL DISCRIPTION:**

With high ability to withstand the shock loading of large current, BTA06 series triacs provide high dv/dt rate with strong resistance to electromagnetic interface. With high commutation performances, the products especially recommended for use on inductive load. From all three terminals to external heatsink, BTB06 provides a rated insulation voltage of 2500  $V_{RMS}$ , and BTA06 provides a rated insulation voltage of 2000  $V_{RMS}$ , complying with UL standards (File ref: E252906). All the packages listed are RoHS compliant. (2011/65/EU)

#### **FEATURES:**

| SYMBOL              | VALUE   | UNIT |  |  |

|---------------------|---------|------|--|--|

| I <sub>T(RMS)</sub> | 6       | Α    |  |  |

| $V_{DRM}/V_{RRM}$   | 600/800 | V    |  |  |

# **ABSOLUTE MAXIMUM RATINGS** (Ta = 25 °C Unless otherwise specified)

| PARAMETER                                      |                                               |    | SYMBOL                | VALUE     | UNIT   |

|------------------------------------------------|-----------------------------------------------|----|-----------------------|-----------|--------|

| Storage junction temperature range             |                                               |    | T <sub>stg</sub>      | -40 ~ 150 | °C     |

| Operating junction                             | temperature range                             |    | T <sub>i</sub>        | -40 ~ 125 | °C     |

| Repetitive peak off                            | f-state voltage (Tj=25°                       | C) | $V_{DRM}$             | 600/800   |        |

| Repetitive peak re                             | verse voltage (Tj=25°0                        | C) | $V_{RRM}$             | 600/800   | V      |

| RMS on-state Insulated (T <sub>C</sub> =100°C) |                                               |    | - I <sub>T(RMS)</sub> | -         | Α      |

| current                                        | current Non-Insulated (T <sub>C</sub> =105°C) |    |                       | 6         |        |

| Non repetitive surge peak on-state current     |                                               |    |                       | 60        | Α      |

| (full cycle, F=50Hz)                           |                                               |    | I <sub>TSM</sub>      | 00        | A      |

| I <sup>2</sup> t value for fusing              | (tp=10ms)                                     |    | l <sup>2</sup> t      | 18        | $A^2s$ |

| Critical rate of rise of on-state I-II-III     |                                               |    | dl/dt                 | 50        | Λ/110  |

| current (I <sub>G</sub> =2×I <sub>GT</sub> )   |                                               |    | di/di                 | 10        | A/µs   |

| Peak gate current                              |                                               |    | I <sub>GM</sub>       | 2         | А      |

| Average gate power dissipation                 |                                               |    | $P_{G(AV)}$           | 1         | W      |

| Peak gate power                                |                                               |    | $P_{GM}$              | 5         | W      |

#### THERMAL RESISTANCES

| PARAMETER            | SYMBOL        | VALUE         | UNIT |        |

|----------------------|---------------|---------------|------|--------|

| lunation to appoint  | Insulated     | D             | 2.9  | °C/\\/ |

| Junction to case(AC) | Non-Insulated | $K_{th(j-c)}$ | 2.3  | °C/W   |

# ELECTRICAL CHARACTERISTICS at (Ta = 25 °C Unless otherwise specified)

| 3 Quadrants                                               |                 |                                                                        |                                                        |         |       |            |          |          |      |

|-----------------------------------------------------------|-----------------|------------------------------------------------------------------------|--------------------------------------------------------|---------|-------|------------|----------|----------|------|

| PARAMETER                                                 | SYMBOL          | QUADRANT                                                               | TEST CONDITION                                         |         | VALUE |            |          | ı        | UNIT |

|                                                           |                 |                                                                        | TEOT GONDINON                                          |         | TW    | SW         | CW       | BW       | 0    |

| Gate Trigger Current                                      | l <sub>GT</sub> | $V_D = 12V R_L = 30\Omega$                                             |                                                        | MAX     | 5     | 10         | 35       | 50       | mA   |

| Gate Trigger Voltage                                      | $V_{GT}$        | I-II-III V <sub>D</sub> = 12 V K <sub>L</sub> = 3002                   |                                                        | IVI) UX | 1.5   |            |          | V        |      |

| Off-State Gate Voltage                                    | $V_{\sf GD}$    | $V_{D} = V_{DRM} T_{j}$ $I-II-III = 125^{\circ}C$ $R_{L} = 3.3K\Omega$ |                                                        |         | 0.2   |            |          | V        |      |

| Latabina Current                                          | _               | I-III                                                                  | 1 -1 21                                                | MAX     | 10    | 15         | 50       | 70       | mA   |

| Latching Current                                          | ار              | II                                                                     | $I_G = 1.2I_{GT}$                                      | IVIAA   | 15    | 25         | 60       | 80       | IIIA |

| Holding Current                                           | I <sub>H</sub>  | I <sub>T</sub> =0.2A                                                   |                                                        | MAX     | 6     | 10         | 35       | 60       | mA   |

| Critical Rate of Rise of<br>Off-State Voltage             | dV/dt           | V <sub>D</sub> =2/3V <sub>DRM</sub> Gate Open<br>T <sub>i</sub> =125°C |                                                        |         | 50    | 100        | 400      | 1000     | V/µs |

| Critical rate of decrease of commutating on-state current | (dl/dt)c        | Without sunbber T <sub>j</sub> =125°C                                  |                                                        |         | 1.2   | 2.4        | 3.5      | 5.3      | A/ms |

| 4 Quadrants                                               |                 |                                                                        |                                                        |         |       |            |          |          |      |

| PARAMETER                                                 | SYMBOL          | QUADRANT                                                               | TEST CONDITION                                         |         |       |            | VALUE    |          | UNIT |

| .,                                                        | 01111202        |                                                                        | 1201 00113                                             |         |       | 14414      | С        | В        | 0    |

| Gate Trigger Current                                      | I <sub>GT</sub> | I - II - III<br>IV                                                     |                                                        | 000     |       | MAX<br>MAX | 25<br>50 | 50<br>70 | mA   |

| Gate Trigger Voltage                                      | $V_{GT}$        | ALL                                                                    | $V_D = 12V R_L$                                        | =30Ω    |       | MAX        |          | .5       | V    |

| Off-State Gate Voltage                                    | V <sub>GD</sub> | ALL                                                                    | $V_D = V_{DRM} T_j = 125$ °C<br>$R_L = 3.3$ KΩ         |         |       | MIN        |          | .2       | V    |

| Latching Current                                          | ار              | I - III                                                                | I <sub>G</sub> =1.2I <sub>GT</sub>                     |         |       | MAX        | 50       | 70       | mA   |

|                                                           |                 | II                                                                     | 11 1 3 3.                                              |         |       | MAX        | 60       | 80       | , \  |

| Holding Current                                           | I <sub>H</sub>  |                                                                        | I <sub>T</sub> =0.2A                                   |         |       | MAX        | 40       | 60       | mA   |

| Critical Rate of Rise of<br>Off-State Voltage             | dV/dt           | VD=2/3                                                                 | VD=2/3V <sub>DRM</sub> Gate Open T <sub>j</sub> =125°C |         |       | MIN        | 200      | 500      | V/µs |

# STATIC CHARACTERISTICS

| PARAMETER                 |                       | SYMBOL           | TEST CONDITION                    | VALUE (MAX) | UNIT |

|---------------------------|-----------------------|------------------|-----------------------------------|-------------|------|

| On-State Voltage          | T <sub>j</sub> =25°C  | $V_{TM}$         | $I_{TM} = 8.5 A t_p = 380 \mu s$  | 1.5         | V    |

| Off State Leakage Current | T <sub>j</sub> =25°C  | I <sub>DRM</sub> | \/ -\/ \/ -\/                     | 5           | μΑ   |

| Off-State Leakage Current | T <sub>j</sub> =125°C | I <sub>RRM</sub> | $V_D = V_{DRM}$ , $V_R = V_{RRM}$ | 1           | mΑ   |

An IATF 16949, ISO9001 and ISO 14001 Certified Company

## **TYPICAL CHARACTERISTICS CURVES**

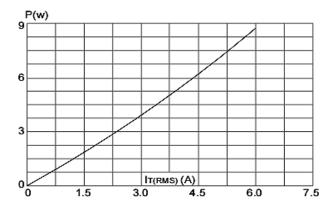

Fig 1: Maximum power dissipation versus RMS on-state current

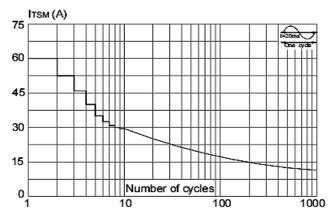

Fig 2: Surge peak on-state current versus number of cycles

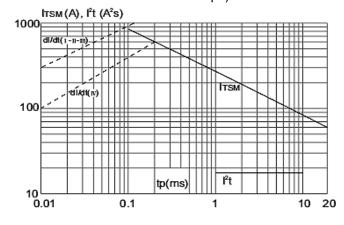

Fig 3: Non-repetitive surge peak on-state current for a sinusoidal pulse with width tp<20ms, and corresponding value of I t (I-II-III:dl/dt < 50A/μs; IV:dl/dt < 10A/μs)

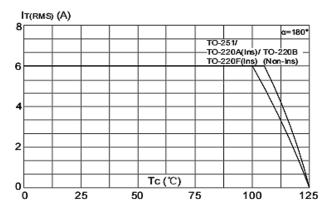

Fig 4: RMS on-state current versus case temperature

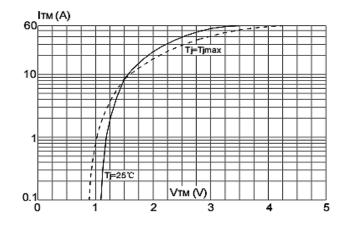

Fig 5: On-state characteristics (maximum values)

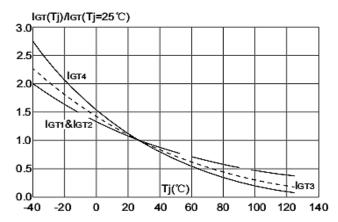

Fig 6: Relative variations of gate trigger current versus junction temperature

# TYPICAL CHARACTERISTICS CURVES

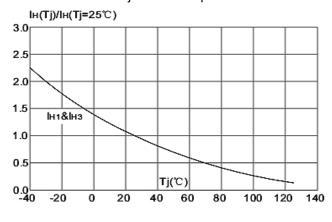

Fig 7: Relative variations of holding current versus junction temperature

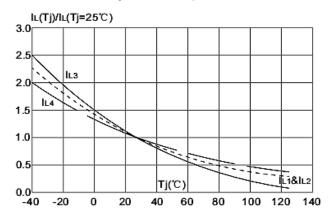

Fig 8: Relative variations of latching current versus junction temperature

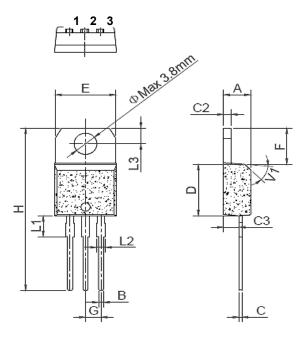

# **PACKAGE DETAILS**

TO-220 Insulated/ Non-insulated Leaded Plastic Package

|      | Dimensions  |             |      |        |      |      |  |

|------|-------------|-------------|------|--------|------|------|--|

| Ref. | Millimeters |             |      | Inches |      |      |  |

|      | Min.        | Min. Typ. N |      | Min.   | Тур. | Max. |  |

| Α    | 4.40        |             | 4.60 | 0.17   |      | 0.18 |  |

| В    | 0.61        |             | 0.88 | 0.02   |      | 0.04 |  |

| С    | 0.46        |             | 0.70 | 0.02   |      | 0.03 |  |

| C2   | 1.21        |             | 1.32 | 0.05   |      | 0.05 |  |

| C3   | 2.40        |             | 2.72 | 0.09   |      | 0.11 |  |

| D    | 8.60        |             | 9.70 | 0.34   |      | 0.38 |  |

| E    | 9.80        |             | 10.4 | 0.39   |      | 0.41 |  |

| F    | 6.55        |             | 6.95 | 0.26   |      | 0.27 |  |

| G    |             | 2.54        |      |        | 0.1  |      |  |

| Н    | 28.0        |             | 29.8 | 1.1    |      | 1.17 |  |

| L1   |             | 3.75        |      |        | 0.15 |      |  |

| L2   | 1.14        |             | 1.70 | 0.05   |      | 0.07 |  |

| L3   | 2.65        |             | 2.95 | 0.1    |      | 0.12 |  |

| V1   |             | 45°         |      |        | 45°  |      |  |

# **Pin Configuration**

- 1. T1

- 2. T2

- 3. Gate

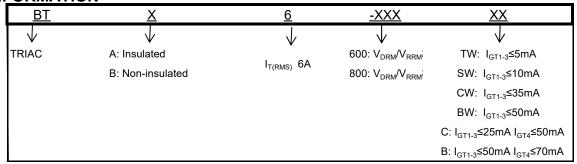

# **ORDERING INFORMATION**

# Recommended Product Storage Environment for Discrete Semiconductor Devices

This storage environment assumes that the Diodes and transistors are packed properly inside the original packing supplied by CDIL.

- · Temperature 5 °C to 30 °C

- · Humidity between 40 to 70 %RH

- · Air should be clean.

- · Avoid harmful gas or dust.

- · Avoid outdoor exposure or storage in areas subject to rain or water spraying .

- · Avoid storage in areas subject to corrosive gas or dust. Product shall not be stored in areas exposed to direct sunlight.

- · Avoid rapid change of temperature.

- · Avoid condensation.

- · Mechanical stress such as vibration and impact shall be avoided.

- · The product shall not be placed directly on the floor.

- The product shall be stored on a plane area. They should not be turned upside down. They should not be placed against the wall.

#### **Shelf Life of CDIL Products**

The shelf life of products is the period from product manufacture to shipment to customers. The product can be unconditionally shipped within this period. The period is defined as 2 years.

If products are stored longer than the shelf life of 2 years the products shall be subjected to quality check as per CDIL quality procedure.

The products are further warranted for another one year after the date of shipment subject to the above conditions in CDIL original packing.

#### Floor Life of CDIL Products and MSL Level

When the products are opened from the original packing, the floor life will start.

For this, the following JEDEC table may be referred:

| JEDEC MSL Level |                    |                 |  |  |  |  |

|-----------------|--------------------|-----------------|--|--|--|--|

| Level           | Time               | Condition       |  |  |  |  |

| 1               | Unlimited          | ≤30 °C / 85% RH |  |  |  |  |

| 2               | 1 Year             | ≤30 °C / 60% RH |  |  |  |  |

| 2a              | 4 Weeks            | ≤30 °C / 60% RH |  |  |  |  |

| 3               | 168 Hours          | ≤30 °C / 60% RH |  |  |  |  |

| 4               | 72 Hours           | ≤30 °C / 60% RH |  |  |  |  |

| 5               | 48 Hours           | ≤30 °C / 60% RH |  |  |  |  |

| 5a              | 24 Hours           | ≤30 °C / 60% RH |  |  |  |  |

| 6               | Time on Label(TOL) | ≤30 °C / 60% RH |  |  |  |  |

An IATF 16949, ISO9001 and ISO 14001 Certified Company

#### **Customer Notes**

#### **Component Disposal Instructions**

- 1. CDIL Semiconductor Devices are RoHS compliant, customers are requested to please dispose as per prevailing Environmental Legislation of their Country.

- 2. In Europe, please dispose as per EU Directive 2002/96/EC on Waste Electrical and Electronic Equipment (WEEE).

#### Disclaimer

The product information and the selection guides facilitate selection of the CDIL's Semiconductor Device(s) best suited for application in your product(s) as per your requirement. It is recommended that you completely review our Data Sheet(s) so as to confirm that the Device(s) meet functionality parameters for your application. The information furnished in the Data Sheet and on the CDIL Web Site/CD are believed to be accurate and reliable. CDIL however, does not assume responsibility for inaccuracies or incomplete information. Furthermore, CDIL does not assume liability whatsoever, arising out of the application or use of any CDIL product; neither does it convey any license under its patent rights nor rights of others. These products are not designed for use in life saving/support appliances or systems. CDIL customers selling these products (either as individual Semiconductor Devices or incorporated in their end products), in any life saving/support appliances or systems or applications do so at their own risk and CDIL will not be responsible for any damages resulting from such sale(s).

CDIL strives for continuous improvement and reserves the right to change the specifications of its products without prior notice.

CDIL is a registered trademark of

#### **Continental Device India Pvt. Limited**

C-120 Naraina Industrial Area, New Delhi 110 028, India.

Telephone +91-11-2579 6150, 4141 1112 Fax +91-11-2579 5290, 4141 1119

email@cdil.com www.cdil.com

CIN No. U32109DL1964PTC004291